3.1 KiB

宣传页封面

主要特点

- DAC 更新率最高12 GSPS

- ADC采样率最高6 GSPS

- AWG支持直接/调制波形输出

- AWG支持标记脉冲输出

- DAQ支持多种数据采集模式

- DAQ支持低延迟反馈控制

- AWG\DAQ支持指令集的编程

简要描述

RBPU16是一款用于量子比特态信息读出的一款SoC芯片, 最大支持16个量子比特态信息并行读出。 芯片内部集成了PLL、ADC、DAC和DSP等模块,其可以利用高速DAC产生微波信号激发读取腔,并通过数字I/O使能外部Pump通道,接着利用高速ADC采集处理反射回来的信号,并通过DSP计算量子态信息,最后将读出的量子态信息通过LVDS接口实时发送出去,为量子比特态信息读出提供高集成度解决方案。

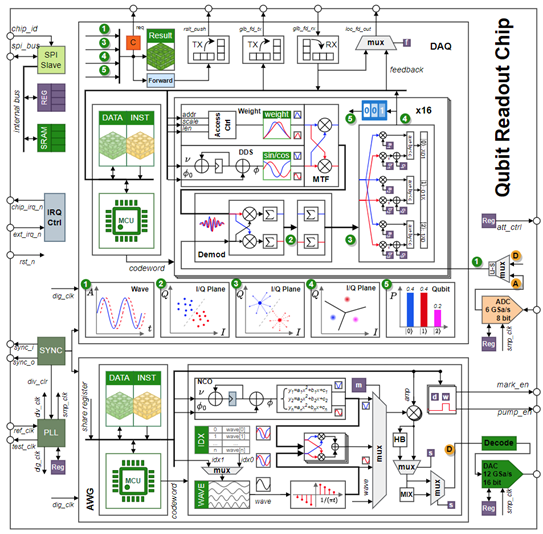

功能框图

1. 规格参数

2. 操作最大值

3. 管脚描述

4. 典型性能特点

5. 专业术语

6. 操作原理

RBPU16是一颗用于完成超导量子比特的态读出的SoC基带芯片。 芯片模拟部分包括ADC、DAC、PLL、LVDS、POR和温度传感器; 数字部分主要包括DAQ、AWG、PlsGen、Feedback以及System模块。 读出芯片的总体功能组成如图 1所示。

在激励信号生成路径上,AWG用于控制激励通道待输出的波形, 接着波形经过DAC转换成基带读出激励信号, 同时AWG模块触发PlsGen模块实时发出脉冲信号使能外部Pump通道。 回波信号处理路径上,ADC用于采集反射的读出基带信号, 接着DAQ对基带信号进行分析处理,结果再通过LVDS接口发送出去, 同时DAQ模块触发Feedback模块将部分结果上报或者下发到外部芯片。 片内PLL用于管理整个芯片的时钟,为ADC生成采样时钟, 为DAC生成更新时钟,为数字模块生成主时钟等。 POR用于在芯片上电时对整个芯片进行复位,保障芯片正常工作。 温度监视模块用于实时监测芯片温度变化,保障芯片稳定工作。 System模块用于管理芯片上控制的状态,为芯片运维和调试提供支撑。

本章节从读出芯片的原理及模块划分、关键数据路径、接口控制协议几个方面进行介绍。 需要注意到的是:读出芯片不仅支持以ASIC芯片模式工作,也支持部分核心控制在FPGA内部工作。 这两种工作模式受制于ASIC和FPGA资源以及外部ADC、DAC硬件性能不同, 部分功能实现存在差异,后续阅读时需要重点关注。

关键数据路径

7. 应用注意

7.1 模拟接口

7.2 启动顺序

为了确保芯片正常工作,需要满足以下启动顺序要求:

- 内核供电上电

- IO供电上电

- 时钟配置完毕

- 芯片复位

8. 寄存器定义

8.1 寄存器摘要

读出芯片偏移地址空间分配如表 2所示,用户可以通过读写相应地址来控制读出芯片功能和访问芯片状态。读出芯片地址空间包含系统配置状态、模拟配置状态、DAQ配置状态、AWG配置状态以及PLL配置状态五个部分。

| 功能划分 | 子模块 | 开始地址 | 空间大小 |

|---|---|---|---|