10 KiB

宣传页封面

主要特点

- DAC 更新率最高12 GSPS

- ADC采样率最高6 GSPS

- AWG支持直接/调制波形输出

- AWG支持标记脉冲输出

- DAQ支持多种数据采集模式

- DAQ支持低延迟反馈控制

- AWG\DAQ支持指令集的编程

简要描述

RBPU16是一款用于量子比特态信息读出的一款SoC芯片, 最大支持16个量子比特态信息并行读出。 芯片内部集成了PLL、ADC、DAC和DSP等模块,其可以利用高速DAC产生微波信号激发读取腔,并通过数字I/O使能外部Pump通道,接着利用高速ADC采集处理反射回来的信号,并通过DSP计算量子态信息,最后将读出的量子态信息通过LVDS接口实时发送出去,为量子比特态信息读出提供高集成度解决方案。

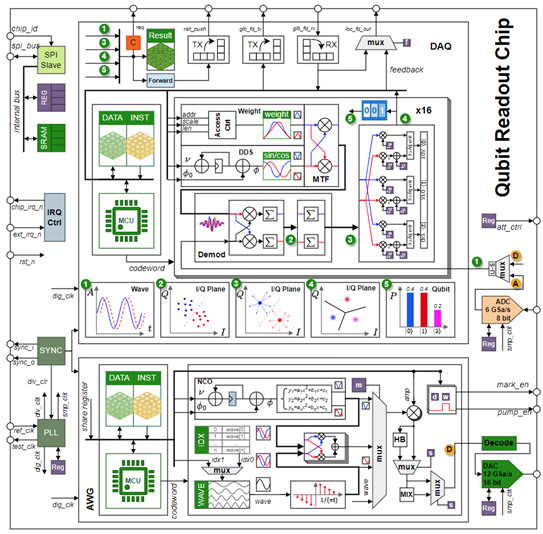

功能框图

1. 规格参数

@import "specification.md"

2. 操作最大值

TODO

3. 管脚描述

TODO

4. 典型性能特点

5. 专业术语

6. 操作原理

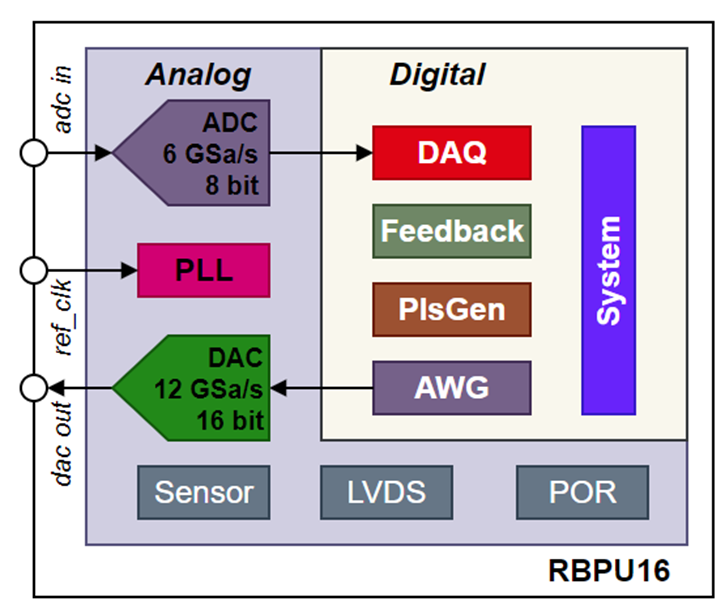

6.1 原理及模块划分

RBPU16是一颗用于完成超导量子比特的态读出的SoC基带芯片。

芯片模拟部分包括ADC、DAC、PLL、LVDS、POR和温度传感器;

数字部分主要包括DAQ、AWG、PlsGen、Feedback以及System模块。

读出芯片的总体功能组成如下图所示。

在激励信号生成路径上,AWG用于控制激励通道待输出的波形, 接着波形经过DAC转换成基带读出激励信号, 同时AWG模块触发PlsGen模块实时发出脉冲信号使能外部Pump通道。 回波信号处理路径上,ADC用于采集反射的读出基带信号, 接着DAQ对基带信号进行分析处理,结果再通过LVDS接口发送出去, 同时DAQ模块触发Feedback模块将部分结果上报或者下发到外部芯片。

片内PLL用于管理整个芯片的时钟,为ADC生成采样时钟, 为DAC生成更新时钟,为数字模块生成主时钟等。 POR用于在芯片上电时对整个芯片进行复位,保障芯片正常工作。 温度监视模块用于实时监测芯片温度变化,保障芯片稳定工作。 System模块用于管理芯片上控制的状态,为芯片运维和调试提供支撑。

本章节从读出芯片的原理及模块划分、关键数据路径、接口控制协议几个方面进行介绍。 需要注意到的是:读出芯片不仅支持以ASIC芯片模式工作,也支持部分核心控制在FPGA内部工作。 这两种工作模式受制于ASIC和FPGA资源以及外部ADC、DAC硬件性能不同, 部分功能实现存在差异,后续阅读时需要重点关注。

6.2 关键数据路径

6.2.1 读出激励输出通道

@import "../readout_program/ri_datapath.md"

6.2.2 读出回波信号处理

@import "../readout_program/ro_datapath.md"

6.3 接口控制协议

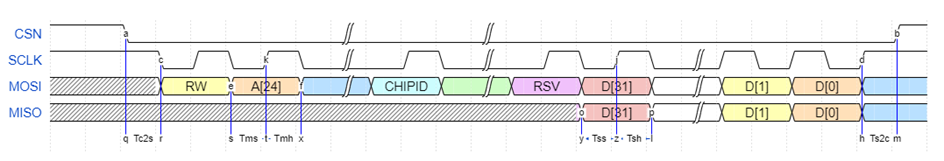

6.3.1 SPI配置协议

读出芯片通过SPI来配置内部寄存器和内存,SPI采用四线模式。

时钟极性CPOL=1,即时钟在空闲时处于高电平状态,

时钟相位CPHA=1,即在第一个时钟沿输出数据,第二个时钟沿采样数据。

SPI的通信数据格式采用自定义协议,支持流模式发送接收,

SPI的通信协议如下图所示:

协议首先发送1比特读写标识位, 然后发送25比特地址位, 接着再发送5比特的芯片选择信号, 最后再发送/接收数据。 标识控制位含义如下表所示。 数据发送/接收以32比特为单位, 以流模式发送, 支持发送/接收N*32位的数据, 直到主控端将csn信号拉低后结束通信, 这里N为大于等于1的整数。 流模式要求从设备在完成32比特数据接收/发送后自动对地址进行4字节递增。

| 字段 | RW | ADDR | CHIP_ID | RSV | DATA |

|---|---|---|---|---|---|

| 位宽 | 1 | 25 | 5 | 1 | 32*N |

| 含义 | 0:读,1:写 | 32 MB寻址空间 | 总线片选 | 保留位 | 数据 |

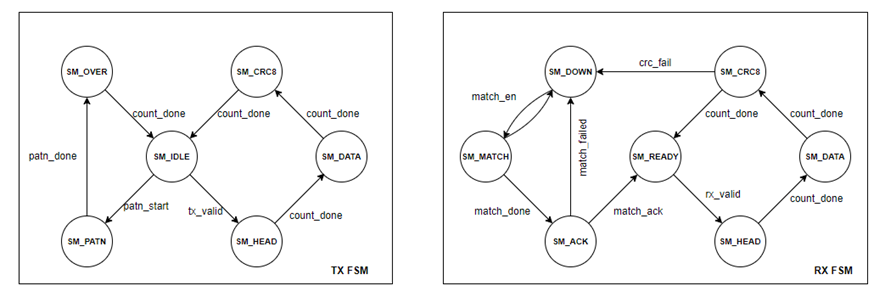

6.3.2 LVDS通信协议

从读出芯片到多功能母卡的数据推送接口rslt_push_[p,n], 反馈上报接口glb_tx_[p,n]和从多功能母板到读出芯片的反馈下发接口glb_rx_[p,n]采用了定制的LVDS通信协议, 协议帧格式如下图所示:

+---------------------------------------+

| LVDS DATA FRAME |

+------+-------------------+------------+

| 4 | 16/32/64/128 | 8 |

+------+-------------------+------------+

| HEAD | Payload | CRC8 |

+-----+--------------------+------------+

MSB LSB

帧头包含4比特数据,其中最高位比特用于指示是否启动数据传输,

次高位置0保留,最低两位用于指示本次传输的数据量。

载荷支持16、32、64、128比特四种数据。

最后采用8比特校验码作为结束,

校验多项式为: x^8 + x^2 + x + 1。

当处于空闲状态不用传输数据时,发送端将LVDS信号电平拉高。 当传输数据时,发送端将LVDS电平拉低两个数据周期启动数据发送, 接着发送两比特数据指示本次载荷数据量, 其中0表示16比特,1表示32比特,2表示64比特,3表示128比特; 帧头发送完毕后紧接着将帧头指示的数据量的数据载荷发送; 最后将载荷计算得到的CRC8校验码发送;

考虑到接收端可能由于信号亚稳态或者串并转换不能正确采集输入数据, 协议要求接收端在接收数据之前必须先和发送端同步。 发送端通过发送同步码来同步接收端, 当完成设定数量的同步码发送完毕后再发送一个结束码结束同步过程。 同步码为字符串”hfnl”对应的32比特数据, 接收码为”exit”对应的32比特数据。

发送和接收的状态机如上图所示, 接收端在启动时会被初始化到未同步状态, 此时必须接收到足够次数的同步码之后才能进入确认状态, 直道接收到确认码之后发送端和接收端会同时进入就绪状态。 接收端后续如果在接收数据过程发现CRC8校验码出错, 接收端会再次进入未同步状态。

7. 应用注意

7.1 模拟接口

7.2 启动顺序

为了确保芯片正常工作,需要满足以下启动顺序要求:

- 内核供电上电

- IO供电上电

- 时钟配置完毕

- 芯片复位

7.3 配置流程

读出芯片在上电后应该校准,校准过程用于完成片上ADC、DAC、PLL以及系统同步,校准过程参考读出子系统运维操作手册。 在实验中读出芯片的操作遵循数据配置、实验运行和数据采集三个阶段。

7.3.1 数据配置阶段

- RO通道配置:外部硬件通过SPI接口对读出芯片的寄存器(包括输出模式,例如直发模式、NCO Only模式、调制模型)、波形查找表、波形仓库、输出MCU控制程序及数据。

- RI通道配置:外部硬件通过SPI接口对读出芯片的寄存器(包括采集模式,例如波形模式、解模模式、态结果模型等)、读出参数、匹配滤波器权重、采集控制程序及数据。

- Pump通道配置:主要配置Pump通道输出的使能信号宽度和相对码字触发的延迟。

若芯片出现异常,在实验配置前应该通过写寄存器来软复位芯片的状态机和寄存器默认值,数据配置用例参考读出子系统历史无关配置集

7.3.2 实验运行阶段

读出芯片的运行通过同步触发信号来启动, 从而确保多个芯片间具有确定的时序关系。 此外考虑到不同类型通信固有延迟不同, 同步信号在芯片内部首先经过同步延迟模块, 同步延迟模块能够为DAQ和AWG分别延迟不同的时间, 从而确保读出芯片的DAQ和AWG模块能够协同运行。

同步信号到达DAQ和AWG模块后,DAQ和AWG模块内部的MCU分别启动运行, MCU从0地址加载指令运行,其按照每三个时钟一个指令的速度执行, MCU根据编程指令修改控制寄存器与发出控制码字, 对于AWG,控制码字驱动波形输出和Pump使能输出, 对于DAQ,控制码字驱动数据采集和反馈上报/下发。 MCU运行到退出指令后,退出运行并进入空闲状态。

7.3.3 实验数据采集阶段

实验数据采集与MCU运行是同时启动的, 如果采集数据量较大,存在MCU运行结束但是数据还没采集完成的情况, 此时数据继续写入到缓存区, 主动数据上报模块继续从缓存中拿取数据并通过数据上报接口推送出去, 当缓存中数据推送完毕后结束实验, 此时可以通过检测推送数据量与目标数据量是否相等, 控制发出读请求信号来指示实验是否完毕。 若不能提前确定采集的数据量, 则只能在MCU运行结束后通过等待一定的时间, 通过检测是否有数据返回来判断实验是否完成。

7.4 异常处理

INT_STATUS寄存器是INT_MASK与对应实际输入状态按位相与再与INS_STATUS本身按位或运算的结果,需要通过命令清零。

8. 寄存器定义

8.1 寄存器摘要

读出芯片偏移地址空间分配如下所示, 用户可以通过读写相应地址来控制读出芯片功能和访问芯片状态。 读出芯片地址空间包含系统配置状态、模拟配置状态、DAQ配置状态、AWG配置状态以及PLL配置状态五个部分。

@import "seg_define.csv"

- 注1:DAQ和AWG各自包含一个MCU模块, MCU模块仅能够访问模块内部的控制器指令、控制器数据和寄存器配置, 访问基地址分别重新映射到了0x000000, 0x100000和0x200000;

- 注2:MCU仅能够显示访问控制器数据和对应寄存器配置数据。 对于控制器指令空间,控制器自动读取指令并运行,无法显式访问和修改数据。

- 注3:匹配滤波器参数和匹配滤波器权重分别对应FPGA和ASIC平台, FPGA平台受限于计算资源有限,采用系数直接存储的方案, 需要额外配置0x580000地址数据,此时0x500000地址中仅包络参数有效。

8.2 操作码字定义

8.2.1 激励输出控制

@import "../readout_program/ri_codeword.md"

8.2.2 采集处理控制

@import "../readout_program/ro_codeword.md"

8.3 寄存器/存储详细定义

读出芯片的详细寄存器/存储定义参考读出芯片IDS表, 相应的驱动软件配置文件参考读出芯片IDS表。